Difference between revisions of "Undocumented LTspice"

m (→B-Sources: added bolding to RndLim) |

(→Introduction: Added directions about submitting change requests) |

||

| Line 1: | Line 1: | ||

== Introduction == | == Introduction == | ||

| + | '''Please submit your requests for additions or changes to ''Undocumented LTspice'' on the "discussion" page (second tab above).''' | ||

LTspice/SwitcherCAD III is a complete and fully functional SPICE program (electronic circuit simulator) that is available free of charge from the Linear Technology Corporation (LTC). Because of its superior performance, excellent community support and ease of file sharing, it is rapidly replacing all other SPICE programs, regardless of price, as the simulator of choice for hobbyists, students and professionals alike. | LTspice/SwitcherCAD III is a complete and fully functional SPICE program (electronic circuit simulator) that is available free of charge from the Linear Technology Corporation (LTC). Because of its superior performance, excellent community support and ease of file sharing, it is rapidly replacing all other SPICE programs, regardless of price, as the simulator of choice for hobbyists, students and professionals alike. | ||

| Line 8: | Line 9: | ||

As to the classification of anything not covered above, you must make your own common sense judgment or ask the advice of the users group moderator or the program author via private email. Clearly any standard, generic SPICE feature that works in LTspice would be okay for general use and discussion regardless of its state of documentation in LTspice. A lot of the standard devices have undocumented parameters (e.g., tempcos) or syntax (e.g., Pspice specific compatibility) that would fall into this category. Just as clearly, any undocumented A-device that is specific to LTC’s encrypted, high performance SMPS IC models would likely be considered proprietary knowledge to be protected with due diligence from release to the public domain, lest LTC’s competitors gain the de facto permission to freely copy them in their own circuit simulator offerings (however, it is difficult to see how LTC could legitimately prevent private individuals from making use of such undocumented features in their own simulations or discussing them via private communications). For these reasons, this last category of undocumented features will not be directly discussed here. | As to the classification of anything not covered above, you must make your own common sense judgment or ask the advice of the users group moderator or the program author via private email. Clearly any standard, generic SPICE feature that works in LTspice would be okay for general use and discussion regardless of its state of documentation in LTspice. A lot of the standard devices have undocumented parameters (e.g., tempcos) or syntax (e.g., Pspice specific compatibility) that would fall into this category. Just as clearly, any undocumented A-device that is specific to LTC’s encrypted, high performance SMPS IC models would likely be considered proprietary knowledge to be protected with due diligence from release to the public domain, lest LTC’s competitors gain the de facto permission to freely copy them in their own circuit simulator offerings (however, it is difficult to see how LTC could legitimately prevent private individuals from making use of such undocumented features in their own simulations or discussing them via private communications). For these reasons, this last category of undocumented features will not be directly discussed here. | ||

| − | |||

== Numerical Accuracy/Dynamic Range == | == Numerical Accuracy/Dynamic Range == | ||

Revision as of 04:03, 19 November 2018

Contents

- 1 Introduction

- 2 Numerical Accuracy/Dynamic Range

- 3 A-Devices

- 4 B-Sources

- 5 G-Sources

- 6 Standard Sources

- 7 Standard Devices

- 8 Dot Commands

- 9 Miscellaneous Hints and Tricks

- 9.1 Alternate Syntax

- 9.2 AKO Aliases (A Kind Of)

- 9.3 Stepping a Model

- 9.4 Schematic Editor

- 9.5 Symbol Editor

- 9.6 Plotting

- 9.7 Probing Subcircuit Waveforms (signal naming conventions)

- 9.8 Netlists

- 10 References & Footnotes

Introduction

Please submit your requests for additions or changes to Undocumented LTspice on the "discussion" page (second tab above).

LTspice/SwitcherCAD III is a complete and fully functional SPICE program (electronic circuit simulator) that is available free of charge from the Linear Technology Corporation (LTC). Because of its superior performance, excellent community support and ease of file sharing, it is rapidly replacing all other SPICE programs, regardless of price, as the simulator of choice for hobbyists, students and professionals alike.

The purpose of this topic is to explore and explain some of the many useful or quirky features that have never appeared in the standard documentation whether due to simple oversight, the feature being considered not important enough, not polished enough or functionally obsolete – or even due to the feature being considered proprietary to another brand of SPICE or to LTspice itself. LTC considers some of these undocumented features as fair game for open discussion in public forums such as the LTspice Yahoo users group, whereas for others, it considers any such open discussions as a violation of its License Agreement.

"Fair game" is any feature that is or has ever been part of the normal distribution, i.e., appears or ever has appeared in the Help file, as plain text in any of the included sample or example files, in any program menu available during normal use of the program, or in any of the materials, presentation files or handouts from any LTspice seminar presentation. Such items are all considered as having been officially "documented" and are specifically allowed as discussion topics in public forums such as the LTspice Yahoo users group. However, be advised that any items that have been dropped from the documentation, even if still functional, should generally be considered obsolete and in risk of being purged from the program code at any time (fortunately, such items are quite rare).

As to the classification of anything not covered above, you must make your own common sense judgment or ask the advice of the users group moderator or the program author via private email. Clearly any standard, generic SPICE feature that works in LTspice would be okay for general use and discussion regardless of its state of documentation in LTspice. A lot of the standard devices have undocumented parameters (e.g., tempcos) or syntax (e.g., Pspice specific compatibility) that would fall into this category. Just as clearly, any undocumented A-device that is specific to LTC’s encrypted, high performance SMPS IC models would likely be considered proprietary knowledge to be protected with due diligence from release to the public domain, lest LTC’s competitors gain the de facto permission to freely copy them in their own circuit simulator offerings (however, it is difficult to see how LTC could legitimately prevent private individuals from making use of such undocumented features in their own simulations or discussing them via private communications). For these reasons, this last category of undocumented features will not be directly discussed here.

Numerical Accuracy/Dynamic Range

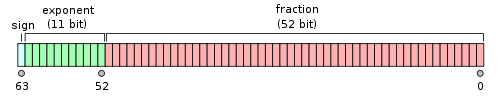

LTspice generally represents numbers using 64 bit double precision arithmetic with the following data structure:

For general component values LTspice will accept numbers that range in magnitude from as large as ± 1.798 x 10+308 down to as small as ± 2.225 x 10−308. Values exceeding this range are interpreted as ± infinity or as zero. However, because of the 52 bit precision of the fractional part of the significand, the practical numerical dynamic range will be circuit dependent. A 53 bit binary significand gives LTspice about 16 significant figures for internal math computations. Thus, if impedances vary by more than 16 orders of magnitude, numerical difficulties may ensue, depending on the topology of the circuit (this is because matrix solving frequently involves differencing two very similar numbers – for example, the next larger number than one is 1.0000000000000002 – anything closer is not resolvable). LTspice's proprietary alternate solver extends this precision by about another 3 orders of magnitude at a cost of a modest speed penalty.

A-Devices

A-devices are Linear Technology Corporation's proprietary special function/mixed mode circuit simulation elements. According to LTspice’s Help file, the behavior of a number of these is undocumented because they frequently change with each new set of models available for LTspice (such changes actually are quite rare and this reason is most likely offered as both as a credible reason for keeping them hidden and to discourage anyone from bothering to attempt to explore and/or use them).

The Help file lists A-device syntax as:

Annn n001 n002 n003 n004 n005 n006 n007 n008 <model> [instance parameters]

Note that all A-devices have up to 8 possible active device connections, up to 5 inputs (terminals 1 through 5) usually 2 outputs (terminals 6 and 7), and with terminal 8 always as the device common. A-devices are always netlisted with the full eight connections. The netlister connects any unused inputs and outputs to terminal 8. The A-device compiler recognizes this condition as a flag that that terminal is not used and removes it from the simulation matrix. Current is sourced or sunk from the outputs (typically the Q or main output on terminal 7 and the Q̅ or complementary output on terminal 6) and is returned through device common, terminal 8.

A-devices are implemented this way to allow a single device type to act as any combination of a 1 to 5 input, 1 to 2 output device, but with no simulation speed penalty for unused terminals. Refer to the program Help file for more details about LTspice’s documented A-devices.

Here is a listing of all known LTspice A-devices.

Documented directly in Help:

- Buf (aka Buf1 Inv)

- AND

- OR

- XOR – when more than two inputs are present, uses the correct definition of true if one and only one input is true, rather than the more common incorrect definition of true if an odd number of inputs are true (which should be called an ODD/NODD gate rather than an XOR/XNOR gate).

- Schmitt (aka SchmittBuf SchmittInv DifSchmitt DiffSchmittBuf DiffSchmittInv)

- Dflop (CLR takes precedence over PRE, also a start up state may be set – see SRflop)

- Varistor

- Modulator (aka Modulate Modulate2)

Not documented in Help but available via the schematic Component Selector:

- SRflop – located in Digital

- PhaseDet (aka PhiDet) – located in Digital

- Counter – located in Digital and documented in the users group (has been officially approved for public use)

- SampleHold (aka Sample) – located in Special Functions

Documented in sample schematics included with the program distribution:

- PhaseDet (aka PhiDet) – located in examples/Educational/PLL2.asc

- SampleHold (aka Sample) – located in examples/Educational/S&H.asc

- OTA – used in UniversalOpamp plaintext subcircuits (in lib/sub), but users group posts (some long standing) containing information about additional aspects of this have been censored

Not documented anywhere by LTC:

- XxxxxxXxxx – prior long standing users group posts about this digital toggle type device have now been censored

- XxXxxXXX – DAC type device never discussed in the users group

- XXXXX – DAC type device never discussed in the users group

- XXXX – DAC type device never discussed in the users group

- Xxx – amplifier type device never discussed in the users group

Not documented anywhere by LTC, but the first two of these devices were extensively documented in the users group. All three devices were eliminated /protected in June 2006 (approximately at release 2.17u ) and all users group posts (some long standing) about these devices have been censored /deleted from the users group archive:

- XXXxxxx – PWM current mode control comparator and latch

- XxxXxx – used for making PWM IC External Oscillators

- Xxxxx – used for making PWM IC oscillators

Obsolete devices that have been deleted from the LTspice executable:

- JKflop

- PGateDrive

- invPGateDrive

- invGateDrive

The three DACs, XxXxxXXX, XxxXXX, XXXX, are specialized A-devices that probably are of little general interest (although their functions and pinouts could likely be easily guessed by examining the data sheets of the few specialized LTC ICs making use of them).

The XXXX seems to be the only straightforward, generic DAC, but very spice-efficient DACs are quite easy to make using standard, approved devices.

SRflop

The Set/Reset Flip-Flop symbol is located in the Digital symbol folder.

- The R (reset) input takes precedence over the S (set) input.

- The start up state of the flip-flop (initial condition) may be specified by adding an "ic=" attribute.

- An "ic" value > Ref interprets to a high, e.g., "ic=1" sets the Q output high and "ic=0" sets it low. (Note: the logic threshold Ref parameter defaults to 0.5 and its use is documented in Help.)

PhaseDet (aka PhiDet)

The Phase Detector symbol is located in the Digital symbol folder.

The Examples folder contains a schematic with some documentation: Examples/Educational/PLL2.asc

SampleHold (aka Sample)

The Sample & Hold symbol is located in the Special Functions symbol folder.

An example schematic, S&H.asc, is located in the Examples/Educational schematic folder.

The behavioral a-device Sample and Hold has two modes of operation. The output may follow the input whenever the S/H input is true or the output may latch to the input when the CLK input goes true. Note that one and only one of these two inputs must be connected.

Parameters unique to the Sample and Hold a-device are as follows:

- Rout defaults to 1kΩ (instead of the standard a-device 1Ω).

- Vhigh defaults to 10V and Vlow defaults to -10V (note: these are output voltage saturation levels).

OTA

The OTA (Operational Transconductance Amplifier) is used in the various UniversalOpamp plaintext subcircuits (located in a standard LTspice program installation in lib/sub).

The default transfer function is a hyperbolic tangent (tanh), which closely approximates the transfer function of a bipolar transistor differential amplifier (this limit can be disabled by adding the flag parameter, Linear). Two differential input pairs are available on pins 1 and 2 ( − + ) and on pins 3 and 4 ( + − ). The transconductance current source output appears on pin 7. As usual, pin 8, if connected, becomes the device's floating "gnd" reference. For reference, a dc "rail" voltage, which represents the maximum possible output (calculated from combining both voltage and current saturation limits), appears on pin 6. This voltage reflects the negative limit only and has an output impedance identical to that of the main output.

Parameters: (default values are zero unless otherwise noted)

- Ref is the input offset voltage

- G (default = 1) is the raw input "gain" (transconductance), where Vdiff = ( Ref – V(1,2) ) * V(3,4) and Iraw = G * Vdiff

- Iout (default = 10u) is the output saturation current, which may be superseded by one or both of

- Isrc (or Isource) is the output sourcing saturation current (= Iout if not specified)

- Isink (a negative number) is the output sinking saturation current (= −Iout if not specified)

- Asym is a flag parameter that, if present, enables independent asymmetrical limits for Isrc/Isource and Isink

- Linear is a flag parameter that, if present, disables output limiting

- Ioffset is the output offset current

- PowerUp (default = true) is a Boolean parameter that if < 0.5 disables all pin 7 output current

- Rout (default = 1/Gmin) is the internal output resistance

- Cout is the capacitance in parallel with Rout

- Vhigh (default = 2) is the positive output "rail" voltage (set to 1e308 to disable limit)

- Vlow is the negative output "rail" voltage (set to −1e308 to disable limit)

- Rclamp (default = 1) is the clamping resistance to the voltage rails

- EN is the voltage noise density

- ENk is the voltage noise knee frequency

- IN is the current noise density

- INk is the current noise knee frequency

- INcm is the common mode (?) current noise density

- INcmk is the common mode (?) current noise knee frequency

Output Current Limit:

- With no flag parameter: Io = tanh ( Iraw / Isat ) * Isat + Idc + Ioffset (note that one limit's action/shape is affected by the opposing limit's magnitude)

where Vdiff = ( Ref – V(1,2) ) * V(3,4) , Iraw = G * Vdiff , Isat = ( Isink – Isrc ) / 2 and Idc = ( Isink + Isrc ) / 2 ; (Isink is a negative number ) - With the Asym flag parameter: Io = if ( Vdiff , tanh ( Iraw / Isrc ) * Isrc , tanh ( Iraw / Isink ) * Isink ) + Ioffset

note that the "if ( <polarity test>, <then action>, <else action> )" conditional statement completely separates the positive and negative limits - With the Linear flag parameter: Io = Iraw + Ioffset (output current does not saturate)

- Note that in all cases the final value of Io is multiplied by buf ( PowerUp )

Output Voltage Limit:

- Clamps through a resistance of Rclamp to "rails" of Vhigh and −Vlow

Noise Voltage Density:

- Vnoise = (EN + IN * Rin_equivalent) * G * Rout

Counter (divide by n):

The Counter symbol is located in the Digital symbol folder (added October 2013).

This device divides the input pulse stream on the CLK input (terminal 1) by the parameter cycles (required) with the divided output pulse stream appearing on the Phi1 main Q output (terminal 7) and the Phi2 complementary Q̅ output (terminal 6). Counting occurs at the rising edge of the pulse stream and duty cycle may be specified. A reset input is available on terminal 2, but this terminal is not present on the standard symbol. Initially and after a reset, the Counter starts high, then goes high again on every Nth edge after that, where N= round(cycles). Note that output behavior is inverted compared to a standard ripple counter.

Parameters unique to the Counter a-device are as follows:

- Cycles divides the rising edge input pulse stream by round(<exp>) where <exp> is the expression assigned to this mandatory parameter.

- Duty specifies the output pulse width = round(cycles*duty). Duty cycle defaults to 0.5 if duty is omitted.

Most of the usual digital a-device parameters may also be optionally applied, e.g., Trise, Vhigh, Vlow, Ref, etc. with the exception of Td, which is ignored (the Counter accepts no delay).

The cycles expression accepts b-source syntax and thus may be a simple constant or may be a complex expression containing constants, parameters, functions, the keyword time, node voltages and branch currents. The Counter output will go to zero whenever the value of cycles falls below 1.5. If the Counter is clocked when the value of cycles is below 1.5, the Counter is reset.

To use this symbol a cycles parameter must be specified after placing the symbol on a schematic (right-click on the symbol to open the "Component Attribute Editor" window and, in the Value attribute field, enter a cycles parameter, e.g. "cycles=2" for a divide by two counter).

A symbol including the reset input and test circuit is available in the online Yahoo LTspice users group: Files/Tut/Digital A-Devices. Alternately, LTspice's standard S/R flip-flop symbol may be used to stand in for the Counter with reset by editing its SpiceModel attribute from "SRFLOP" to "Counter" after it has been placed on the schematic (S becomes the clock input, R becomes the reset input and Q and Q̅ become the two outputs).

B-Sources

While many b-source features were not documented until relatively recently (~2007), most are now at least touched upon in Help and the few that are not are covered in the B sources (complete reference) in this wiki.

- Cpar In addition to the parameter Rpar (which is documented in Help), current source type behavioral sources (i.e., "I=" "R=" and "P=") now accept the Cpar parameter to specify a parallel capacitance. Current derived b-sources driving one ohm in parallel with a small capacitance (e.g., Rpar=1 Cpar=1n) are much more convergence friendly than stiff voltage sources and should be used whenever possible. Nortonizing voltage sources to current sources in parallel with one ohm requires no conversion calculation, but the Nortonized parallel impedance may be set as low as desired if the current source gain is up scaled to compensate.

- Bn P=f(...) Arbitrary Power Sink/source where f is a constant or is an arbitrary function of any valid node voltage, branch current, etc. as with standard b-sources (note: power is sourced when f is negative). In order to avoid large currents at voltages near zero, the arbitrary power sink/sources foldbacks to resistive behavior when the absolute value of voltage across the device falls below a default value of 1 volt. The foldback point may be modified by specifying a VprXover parameter for the device, e.g. VprXover=50mV.

- Bn R=f(...) Arbitrary Resistor where f is an arbitrary function of x (which has the special meaning of the voltage across R in this context) and/or any valid node voltage, branch current, etc. as with standard b-sources.

- [[units] Freq=<valuelist> [delay=<value>]] (Pspice compatible format)

The transfer function of the Freq circuit element is specified by an ordered list of points of freq(Hz), mag(dB) and phase(deg) as follows: <(f1,m1,p1)[(f2,m2,p2)...]> where f1<f2<f3, etc. The following units specifiers may optionally precede the Freq keyword: “rad”=radians, “mag”=non dB, (“dB” and “deg” return the defaults), “r_i”=real and imaginary in place of magnitude and phase. If a delay value is called out, the phases of the table values are modified to reflect the delay (delay is automatically adjusted to maintain causality in any case). - NoJacob The optional NoJacob flag parameter unburdens a device from carrying the mathematical overhead of a Jacobian. For linear or certain well behaved b-source expressions, this small reduction in computational burden can reduce run times slightly. Use with extreme caution, as this greatly increases the risk of creating convergence problems or other errors if misapplied.

- ~ Boolean operator: convert succeeding expression to Boolean then invert

- == Boolean operator: true if preceding expression is equal to succeeding expression, otherwise false

- boltz Boltzmann constant = 1.38062 e-23

- planck Planck's constant = 6.62620 e-34

- echarge Charge of an electron = 1.6021765 e-19

- kelvin Absolute Zero in degrees C = -273.150

- Gmin Minimum conductance = 1e-12 (or as set in the Control Panel or via an .option statement)

- Gmin is added to every PN junction to aid convergence and is the default off-conductance for current or voltage controlled switches and LTspice's idealized diode model.

- square(x) Function = x**2

- tbl Alternate function name, aka table (look-up table)

- stp(x) Alternate function name, aka u(x) (unit step)

- fra(x) Function, very similar to white(x), but = 0 if not SMPS in steady state condition

- UpLim(x, pos, z) Function, similar to Min(x, y), but "z" defines a zone with quadratic soft limiting (note: "x" and "pos" are not strictly interchangeable and "z" must be the end argument)

.func UpLim(x, y, z) if(y-x < z, y - z*exp((y-x-z)/z), x) ; this is UpLim's equivalent mathematical function

- DnLim(x, neg, z) Function, similar to Max(x, y), but "z" defines a zone with quadratic soft limiting (note: "x" and "neg" are not strictly interchangeable and "z" must be the end argument)

.func DnLim(x, y, z) if(x-y < z, y + z*exp((x-y-z)/z), x) ; this is DnLim's equivalent mathematical function

- UpLim(DnLim(x, neg, z_dn), pos, z_up) Composite function, similar to Limit(x, neg, pos), but with up and down soft limit zones (note: arguments are not commutative)

.func RndLim(x, neg, pos, z)= UpLim(DnLim(x, neg, z), pos, z)

- As with the hard limit functions, any or all arguments may be constants or functions of time, node voltages, branch currents, etc.: UpLim(13, V(1,2)*I(Vs), Min(time**2, 5)).

- When their soft limits are greater than zero, these functions have continuous derivatives for superior dc convergence over Min(), Max() and Limit().

- Outside their soft limit zones these functions are perfectly linear which may make them superior to tanh() as a smooth limit function in amplifier macro-modeling applications.

Note that LTspice can execute behavioral sources in either 2G6, PSpice, or Berkeley SPICE syntax in addition to its own enlarged set of behavioral language.

G-Sources

G-Sources have two additional parameters, Vto (threshold) and dir (direction)

Here is the equivalent function:

.func Gsq(x, gain, Vto, dir)=

+ gain*if(dir==0, x, sgn(dir)*uramp(sgn(dir)*(x-Vto))**2)

where x=V(nc+,nc-), the control voltage per the usual G syntax notation from Help:

Gxxx n+ n- nc+ nc- <gain>

Here is a component where this feature is used, along with conventional G-Sources LTC6268

Standard Sources

Add documentation for data file input and triggered sources and the Pspice compatible behavioral forms for E and G sources (at some point, perhaps ~2007, these were added to Help).

Piecewise Linear Sources (PWL)

LTspice supports many more forms of the PWL statement than given in the documentation. LTspice is largely compatible with other SPICE versions, providing similar or identical PWL features.

The non-documented PWL statements can be added on a schematic by first adding a normal source from the Component library, and using the Advanced setting of the source to set the function of the source to one of the two available PWL functions. Once the source is placed on the schematic a right-click on the PWL statement allows to edit it. Once the PWL statement has been changed to a non-documented PWL statement it can also be edited by right-clicking on the component symbol. The right-click will then no longer bring up the special window for changing a source function, but the generic component attribute editor. The PWL statement goes into the value field.

The principle form of the PLW statement is

PWL [VALUE_SCALE_FACTOR=<vsf>]

[TIME_SCALE_FACTOR=<tsf>]

[TRIGGER <trigger expression>]

The functions of the scale factors are obvious. When given, each value or time in the is multiplied by them. The default for each factor is 1.

The is very flexible. Data can either be provided directly in the statement, or by referring to a file (these are documented features). Further, data can be specified so it is repeated a number of times, or forever (both undocumented). Also, data can be specified in a relative way (undocumented). And finally, specifications can be combined to a certain extent (undocumented).

The simplest form of a is a list of one or more data points. Each point is a pair of a time <tx> and a value <vx> values. A pair can, but need not be, grouped together by brackets. Using brackets simplifies the reading of longer lists. Also, commas can be used to separate and group data points.

PWL <t1> <v1> <...> <tn> <vn> PWL (<t1> <v1> <...> <tn> <vn>) PWL (<t1> <v1>) <...> (<tn> <vn>) PWL <t1>, <v1> <...> <tn>, <vn>

The usual suffixes, like m for milli or 'k' for kilo can be used both for times and values, e.g.:

PWL (0m 1 1m 2 1m 3 4m 2)

A value <vx> can also be an expression in curly brackets. However, while function names like sin() are recognized, the keyword time is not. This makes it difficult, probably impossible, to generate time-dependent data, like {sin(time)} or {rand(time)} (to generate random noise)[1].

PWL (0 {sin(1)}) (1 {sin(2)})

Time values <tx> can be specified as relative to the previous time value, by prefixing the value with a + sign, e.g. specifying values at 0, 1, 2, and 7 seconds:

PWL (0 1 +1 2 +1 3 +5 2)

Instead of placing the values directly into the PWL statement they can also be placed in a file, and the file referred in the PWL statement

PWL file=<name of the file>

A list of data points or a file reference can be repeated a fixed amount of times <n>, or forever

PWL REPEAT FOR <n> (|<file spec>) ENDREPEAT PWL REPEAT FOREVER (|<file spec>) ENDREPEAT

E.g. to repeat a sequence of values for five times

PWL REPEAT FOR 5 ( 0 1 1 1 2 2 3 1 ) ENDREPEAT PWL REPEAT FOR 5 ( file=<name of file> ) ENDREPEAT

Data specifications can be combined, e.g:

PWL (0 0 1 1 2 1 3 0) REPEAT FOR 5 (file=<name of file>) ENDREPEAT PWL REPEAT FOR 7 (file=pwl_data.txt) ENDREPEAT REPEAT FOR 6 (file=pwl_data2.txt) ENDREPEAT

Repeat statements can be nested, e.g.:

PWL REPEAT FOREVER (0 1 1 2) REPEAT FOR 3 (2 3 3 1) ENDREPEAT ENDREPEAT

The <trigger expression> turns the source's output on as long as the expression is true. For example, if there is a node n001 in the circuit, the following will turn the output on as long as the node's voltage is greater 1.5V. A source that is turned off is 'stuck' at the first value given in its specification. In the following example the first pair is (0 0), i.e. a value of 0 at time 0. Therefore, when turned off, the source will be stuck at 0.

PWL ( 0 0 1 1 2 1 3 0) TRIGGER V(n001)>1.5

Standard Devices

Diodes: Sidewall Parameters

LTspice (04/05/10) now supports the following diode sidewall parameters:

- perim: Sidewall perimeter (periphery) ; default value = 0m.

- Isw: Sidewall saturation current ; default value = 0A.

- Ns: Sidewall junction emission coefficient ; default value = N (I when Level=11)?

- Rsw: Sidewall series resistance ; default value = 0 ohm.

- Cjsw: Sidewall zero-bias capacitance ; default value = 0.9F * perim?

- Vjsw: Sidewall junction potential ; default value = Vj (1 when Level=11)?

- Mjsw: Sidewall grating coefficient ; default value = 0.33.

- Fcs: Sidewall forward-bias depletion capacitance coefficient ; default value = 0.5 (Fc when Level = 11)?

BJTs: Additional Gummel-Poon Parameters

Bipolar CB avalanche breakdown is modeled in the LTspice Gummel-Poon device:

- BVcbo: C-B breakdown voltage.

- nBVcbo: breakdown emission coefficient ; default value = 1?

- TBVcbo1: linear temperature coefficient of breakdown voltage.

- TBVcbo2: quadratic temperature coefficient of breakdown voltage.

Bipolar BE breakdown is also in the LTspice Gummel-Poon device:

- BVbe: B-E breakdown voltage.

- IBVbe: breakdown current at breakdown voltage.

- nBVbe: breakdown emission coefficient.

VDMOS: Breakdown and Sub-threshold Enhancements

LTspice now contains a number of otherwise undocumented parameters to enhance its proprietary VDMOS model. These allow for body diode breakdown and subthreshold conduction with independent fits to the saturation and linear regions of the output characteristics.

- BV: breakdown voltage.

- IBV: breakdown current at breakdown voltage.

- nBV: breakdown emission coefficient.

- Mtriode: A conductance multiplier for the triode region. It allows independent matching of the saturation and linear regions of the MOSFET.

- subthres: The current (per volt Vds) at which the square-law drain current verses Vgs switches over to exponential.

VDMOS Capacitance (Cgd Curve Fit Equation)

LTspice Help outlines how LTspice generates the VDMOS nonlinear gate-drain capacitance, presenting the general form of the equations used, but it does not reveal the details of the parameters used by the fit equations. Help states that the capacitance expression fit uses two expressions, one for negative gate-drain voltages and another for positive. These expressions meet at zero voltage and it may be assumed that at this point, they must be identical in value and slope. This reduces the system to two equations in two unknowns, allowing a solution for the remaining fit parameters to be obtained. For the following equations, "s" is the slope at the zero point, "y" is the offset and "x" is the gate-drain voltage (not the drain-source voltage).

- Positive gate-drain voltage region: Cgd = s * tanh(a*x) + y (inversion region - switch is on)

- Negative gate-drain voltage region: Cgd = s * atan(a*x) + y (Vds large - switch is off or turning off)

Where s = (Cgdmax - Cgdmin)/(1 + Pi/2) and y = Cgdmax - s and "a", Cgdmax and Cgdmin are existing VDMOS model parameters.

Note that in Help the unspecified parameters are given as A, B, C, and D. These parameters are equivalent to s and y as follows: A = C = s and B = D = y.

Capacitors

Capacitor Multipliers

Capacitors allow an alternate form for the device multiplier m=<value> (number of units in parallel - see Capacitors in Help). In place of "m=<number>", "x<number>" may be used, i.e.: x2, x 2, x0.5, x3.14159. Note that whitespace may optionally separate the leading x and the following number.

Inductors

Maximum Coupling Factor

In LTspice, it is not really possible to set the winding coupling factor (K) exactly to unity. A little experimentation reveals this number to be 1-1n=.999999999. For 1-1n < k <=1, LTspice sets k=1-1n, never informing the user, not even in the error log where the netlist has been flattened and abstract expressions have been converted to numerics.

If k is set to greater than one, LTspice issues a warning that k has been reduced to one (which actually is 1-1n). However this action is not reflected in the netlist nor in the error log's digested netlist.

Resistors

Behavioral Resistors

Create a behavioral resistor by right-mouse-button clicking on its Value field and edit its value to read: R=<expression>. This feature is undocumented, but is considered permissible to use. The expression syntax is the same as for a general behavioral source (see B-sources in Help).

The resistance must not go to zero and negative values can lead to convergence problems, so it is advisable to restrict its values to within a meaningful range as per the following Value example:

R = limit(1,100k,V(1,2)*I(V1)) ; R stays between 1 ohm and 100k

To plot an I-V curve, start by using the differential cursor to plot the voltage across the resistor. First click and hold down the left-mouse-button (red probe icon) on one side of the resistor and then drag and drop the black probe icon on the other side. Finish by dragging the mouse pointer over the x-axis (a ruler icon will appear) and the click the left mouse button to bring up the Horizontal Axis menu. Change the Quantity Plotted from "time" to "I(R1)" (assuming R1 is your behavioral resistor).

Dual Value Resistors (for ac analysis)

LTspice is like Hspice in that it allows resistors to have different dc and ac values. If ac=<value> is specified as a resistor parameter (either immediately after the normal dc value or in the Value2 field), the operating point is calculated using the dc value of resistance, but the ac resistance value is used in the ac analysis. This may be useful when analyzing operational amplifiers, since the operating point computation can be performed on the unity gain configuration using a low value for the feedback resistance and the ac analysis may then be performed on a nearly open loop configuration by specifying a very large value for the ac resistance.

Resistor (and Capacitor) Model Statements

It's not in the .model section of the Help file, but LTspice seems to recognize standard model statements for resistors (RES) and capacitors (CAP), but not inductors (IND).

As in many other SPICE simulators, "RES" and "CAP" are allowed as model keywords. For example, with the following line of spicetext

.model X7R cap (T_measured=20 Tc1=0 Tc2=-19u)

on a schematic, if a capacitor then has "X7R" entered into its "SpiceModel" field (via ctrl-right mouse click) its base value will be multiplied by the following temperature factor, TF

TF = 1 + Tc1*(T-Tmeasured) + Tc2*(T-Tmeasured)**2 where T = the global temperature TEMP or the local instance if specified.

I haven't checked if higher order factors are accepted or if voltage or current factors can be used (they work for some other SPICEs).

The Help file specifies the optional instance of [temp=<value>] syntax for resistors, capacitors and inductors, but only for capacitors does it define this as "instance temperature (for tempcos in a corresponding .model statement)," although nothing further about the model syntax is mentioned.

The help file does not document the "noiseless" control parameter which applies to the resistance in many LTspice circuit elements with resistive elements (resistors, switches, RC lines, others). As its name suggests, this parameter blocks its applicable element's contribution to noise calculations.

Lossy Transmission Lines

There are two undocumented lossy transmission line models implemented in LTspice. One is CPL model (P device), and the other is TXL model (Y device).

The undocumented CPL is a KSPICE-like element, which in theory should be similar to the RLGC model, but without frequency dependent loss (neither skin effect and nor frequency dependent dielectric loss). It also has at least one bug causing an incorrect output voltage offset (a workaround is to only use signals with no dc offset).

Below are example netlists from Kspice, which have been translated as required (very little) into LTspice syntax.

****** test circuit for CPL transmission line simulation ******* * M1 0 268 299 0 MN0P9 w=18u l=1u M2 299 267 748 0 MN0P9 w=18u l=1u M3 0 168 648 0 MN0P9 w=18u l=0u9 M4 1 268 748 1 MP1P0 w=36u l=1u M5 1 267 748 1 MP1P0 w=36u l=1u M6 1 168 648 1 MP1P0 w=36u l=1u * CN648 648 0 25f4 CN651 651 0 7f4 CN748 748 0 25f4 CN751 751 0 9f4 CN299 299 0 5f4 * P1 648 748 0 651 751 0 Pline * vdd 1 0 DC 5 Vk 267 0 DC 5 * *Vs 168 0 PWL (4 15n9 0 16n1 5 31n9 5 32n1 0) *Vs 268 0 PWL (4 15n9 0 16n1 5 31n9 5 32n1 0) * Vs1 168 0 Pulse (0 5 15n9 0n2 0n2 15n8 60n) Vs2 268 0 Pulse (0 5 15n9 0n2 0n2 15n8 60n) * .tran 0n2 47n9 0 1n .model Pline CPL + R=0.2 0 0.2 + L=9n13 3n3 9n13 + G=0 0 0 + C=365f -90f 365f + Length=24 ********************** MODEL SPECIFICATION ********************** .model MN0P9 NMOS Vto=0.8 Kp=48u Gamma=0.30 Phi=0.55 Lambda=0 + Cgso=0 Cgdo=0 Cj=0 Cjsw=0 Tox=18u Ld=0 .model MP1P0 PMOS Vto=-0.8 Kp=21u Gamma=0.45 Phi=0.61 Lambda=0 + Cgso=0 Cgdo=0 Cj=0 Cjsw=0 Tox=18u Ld=0 .end ******* test circuit for TXL transmission line simulation ******* M5 0 168 2 0 MN0P9 w=18u l=0u9 M6 1 168 2 1 MP1P0 w=36u l=1u Cn2 2 0 25f4 Cn3 3 0 7f4 Y1 2 0 3 0 Ymod Vdd 1 0 dc 5.0 Vs 168 0 Pulse (0 5 15n9 0n2 0n2 15n8 32n) *Vs 168 0 PWL(15n9 0 16n1 5 31n9 5 32n1 0) .tran 0n2 47n 0 0n1 .model MN0P9 NMOS Vto=0.8 Kp=48u Gamma=0.3 Phi=0.55 Lambda=0 + Cgso=0 Cgdo=0 Cj=0 Cjsw=0 Tox=18u Ld=0 .model MP1P0 PMOS Vto=-0.8 Kp=21u Gamma=0.45 Phi=0.61 Lambda=0 + Cgso=0 Cgdo=0 Cj=0 Cjsw=0 Tox=18u Ld=0 .model Ymod Txl R=12.45 L=9u G=0 C=0p47 Length=16 .end

Voltage Controlled Switches

LTspice has a cleaner syntax for voltage controlled switches, but has no problem with any PSpice voltage controlled switch syntax.

Dot Commands

.Ac (ac analysis)

In an ac analysis, it seems that the maximum number of points that may calculated is limited to about 65k. If more are requested, LTspice will reduce the point count to this maximum, but without generating an error or warning. This limitation may become significant when attempting to simulate very high Q circuits over too broad a frequency range (e.g., crystal oscillators showing overtones).

.Options

Note: ".opt" is accepted as shorthand notation for ".options" (options are added as text onto the schematic as a SPICE Directive).

There are a whole lot of .option parameters and other control parameters (mostly legacy from SPICE 2 and Pspice) that should be documented (a few probably actually could be useful). Many of these are listed in the LTspice Yahoo group message #20174.

.options List

This flag parameter causes a dump of the flatened netlist (after expanding subcircuits) to appear in the SPICE Error Log file (sticky and causes the corresponding Generate Expanded Listing option check box in Operation tab of the Control Panel to become checked).

.opt List ; selects "Generate Expanded Listing" in the Control Panel

.options DampInductors=<value>

This has the same effect as unchecking (value=0) or checking (value=1) the Rpar inductor option on the Hacks tab of the Control Panel, overriding whatever is set there (the default value in LTspice is 1 or ON, which is opposite the standard SPICE convention). The default value for the parallel damping resistance equals 1e12 times the inductance value (1T x L) and is only applied in the case of a transient analysis.

.opt DampInductors=0 ; turn off LTspice's default parallel damping resistance

.options Thev_Induc=<value>

This has the same effect as unchecking (value=0) or checking (value=1) the Rser inductor option on the Hacks tab of the Control Panel, overriding whatever is set there (the default value in LTspice is 0 or ON, which is opposite the standard SPICE convention). The default value for the series damping resistance equals 1 milliohm and is applied to all analyses.

.opt Thev_Induc=1 ; turn off LTspice's default 1 milliohm series damping resistance (R = 0)

Notes:

- Using the standard SPICE convention settings for these two inductor options causes the circuit matrix to be bigger, run slower and be more prone to convergence errors.

- I have yet to discover how to alter the global default enabled values for Rpar and Rser (changing Gmin has no effect on the parallel damping resistance for inductors).

.options Gfarad=<value>

Added at LTspice version 4.14h (per public posting by Yahoo LTspice group moderator, Helmut Sennewald, 04/13/12).

This option allows the user to set the global value for a capacitor's default parallel conductance factor (1/Rpar = Gpar = Gfarad*C).

.opt Gfarad=1e-12 ; has no effect because this is the existing default conductance factor .opt Gfarad=0 ; sets the global conductance factor to zero (removes the hidden default parallel resistance for all capacitors)

Notes:

- As a convergence aid, capacitors in LTspice include a hidden default parallel resistance of Rpar = 1e12/C. Specifying any value for Equiv. Parallel Resistance (Rpar) in a capacitor's Component Editor window will override this default. Specifying a value of zero (Rpar=0) removes the default resistance (sets the conductance to zero).

- The arbitrary capacitor (specified via a behavioral charge equation - refer to the topic in Help) has no parallel conductance and is not affected by Gfarad.

.options Gfloat=<value>

This option allows the user to set the global value for the shunt conductance from floating nodes to ground.

.opt Gfloat=1e-12 ; has no effect because this is the existing default conductance factor (which is Gshunt) .opt Gfloat=0 ; sets the global conductance factor to zero (removes the hidden default ground shunt resistance for all floating nodes)

Notes:

- As a convergence aid, floating nodes in LTspice include a hidden default shunt resistance to ground. The default value is equal to the value of Gshunt (which also may be optionally set - refer to the topic in Help). Specifying a value for Gfloat will override this default. Specifying a value of zero removes the default shunt resistance (sets the conductance to zero).

- Floating nodes are typically created when only connected to capacitors and/or current sources.

.options TopologyCheck=2

Listed in the ChangeLog 09/14/11: "Beta Optimisations regarding dangling nodes."

Setting this parameter to 2 has the same effect as checking Enable beta circuit matrix optimizations on the Hacks tab of the Control Panel, overriding whatever is set there.

.opt TopologyCheck=2 ; (parameter numbers 0 and 1 are documented in Help)

.options tSeed=<value>

This option lets you seed the integrator with a specific guess for the initial .tran timestep

.opt tSeed=100n

.NodeAlias <aliasName> <netName>

Listed in the ChangeLog 10/06/10: "Allows to give a net an alternative name."

Placing the Jumper symbol (lib/sym/Misc/jumper) is another, documented and probably more convenient way of giving the same net two names, however, in a hierarchical design, it only functions on a top level schematic.

.nodealias output drain

Miscellaneous Hints and Tricks

... should be added here or given its own section if warranted.

Here's a hint to anyone wishing to keep up-to-date with the latest additions to LTspice's great features - always read the changelog.txt file (located in the LTspiceIV program folder) after every web update /sync release.

- From the ChangeLog on 02/21/07: "Added a check box on the Tools=>Control Panel=>Hacks! pane to allow the MC generator to be reseeded by the real time clock."

A-Devices See message #19378 from the LTspice Yahoo users group.

Alternate Syntax

In many contexts, where possible, LTspice supports alternate syntaxes compatible with other simulators.

- Single quotes generally may be used in place of curly braces.

AKO Aliases (A Kind Of)

Suppose I wished to modify a single parameter of an existing model but don't want to copy the full model out as a duplicate and adjust it. I want to pick up all of the specified and default parameter values for the given model name (and if it specifies yet another, to pick up those, as well) and simply modify one parameter or two in a new model.

A reason I may wish to do this is that I may, at some later time, decide to modify the underlying model and I'd like all of the dependent models to pick up the underlying changes, automatically. I just don't know if there is syntax for it. Do you know?

Yes. Try something like this:

.model 2N2222mod ako: 2N2222 bf=5 ; same except lower beta

> It appears that parameters must ultimately resolve to numbers instead of text.

You are correct in your supposition - parameters must be numbers.

> Is there a way to pass text to a subcircuit to do what I want?

Yes. Models can take numeric alias using the AKO ("A Kind Of") function. These numeric aliases will work with parameter passing:

.model 1 ako:2N3904 ;the existing 2N3904 model now also known as "1" .model 2 ako:2N2222 ;the existing 2N2222 model now also known as "2"

This topic has been discussed many times in this forum before, but it may be difficult to search for because the name of the AKO function doesn't really correspond to "Also Known As" (it stands for "A Kind Of").

You can find many examples using AKO in the Group archive here:

Files -> Tut -> Stepping to the max

Stepping a Model

Sometimes it might be of interest to try out several different types of some component in a circuit, instead of just stepping a single parameter of a component. This can be done by giving the models that should be tried number-only names. For example, using the above discussed AKO feature, NPN transistors can be named as follows:

.model 3904 ako:2N3904 .model 2222 ako:2N2222 .model 547 ako:BC547

It is also possible to define a model with a number-only name from scratch:

.model 4 NPN

The next step is to add a spice directive to define a parameter, STM in the example below, which is stepped through the model names. Since the .step command can only step numeric values it is vital that the models have been given number-only names, as shown above.

.step param STM list 3904 2222 547 4

The last step is then to use the parameter in place of a model Value. To make sure the parameter is evaluated, it needs to be placed in brakes. For example, the above defined parameter STM would be given in the form of {STM} as the Value of an NPN transistor symbol.

Schematic Editor

Key Combination

- Shift-Ctrl-Alt-R: Permanently renumbers all reference designators within the schematic.

- Shift-Ctrl-Alt-H: Temporarily highlights all hidden text within the schematic.

- Hold down Ctrl when placing wires to route at any angle.

- Hold down Ctrl when drawing lines to draw off grid.

- Hold down Ctrl or Shift for more movement with arrow keys.

- Hold down Ctrl and Shift for most movement with arrow keys.

- Text preceeded with an underscore ("_") character will be displayed as overbarred (for active LOW digital signals).

Operating Point Data Labels (visible numeric dc bias values)

LTspice has the ability to display dc operating point voltages, currents and expressions (e.g., power, energy, efficiency, etc.) directly within the schematic. Normally, labels are placed upon wires (nodes) much like Net Labels.

Preparation

To be able to place/show operating point data labels right-click on an empty area of the schematic and select "View" from the drop down menu list.

- Checking "Show .op Data Flags" shows all operating point numerical information on the schematic.

Further, in the main menu

- Checking "Mark Unconn. Pins" (main menu -> View) shows anchor boxes on the schematic when a label is moved.

Creating a Label when doing a .op Simulation

When doing a DC operating point simulation (.op) an operating point data label can be created as follows

- Run the .op simulation

- Left-Click on a net (a wire). This creates a new label that can be placed with the cursor.

Creating a Label when doing another Simulations

When doing other kinds of simulations than a DC operating point simulation (.op) operating point data labels can be created by right-clicking on an empty area of the schematic, then selecting View->Place .op Data Label on the drop down menu. The new label can be attached to a net with the cursor.

Format and Layout

Once placed, an operating point data label may be freely moved or copied and then edited to be completely unrelated to the original node. It is of course possible to decorate a label by using the normal drawing functions. For example painting a rectangle around it (main menu Edit->Draw->Rectangle) or by placing some text nearby (main menu Edit->Text).

Operating point data labels default to the display of the voltage of the node to which they are attached (signified by the dollar sign character "$"), but this may be edited to be any valid expression, including currents, powers or even the voltage of a specific node. Right-clicking on a operating point data label brings up a popup window for selecting the data to display or enter an expression.

With fractional values, all available non-zero digits will be displayed, often resulting in unwanted numerical clutter. The number of visible digits may be aesthetically limited by appropriately editing the expression to be displayed. Examples of rounding expressions used for formating:

round($*1k)/1k ; display no more than 3 digits (typically automatically expressed in engineering format). round(I(R1)*1k)/1k ; same display format as above, but expression is of the current through R1. round(V(1,2)*1k)/1k ; same format, but expression is of the voltage difference between nodes 1 & 2.

Bussing of Connections and Components (BUS shorthand notation)

LTspice has an undocumented feature to draw busses (groups of nets) on the schematic. This feature is erratic. It is recommended to double check the resulting circuit by studying the netlist (main menu View->SPICE Netlist), because it is possible to attach wires to busses without exactly knowing which signal (net) from the bus the wire should actually represent. Busses are purely cosmetic on the schematic, they have no special SPICE function. All bussing notation is resolved (flattened to normal net notation) by the schematic editor prior to the creation of the SPICE netlist (the netlister does not understand bus notation, i.e. it it not possible to use a SPICE deck with bus notation in LTspice).

An alternative to busses is to use individual net labels to connect distant nets.

A net (wire) becomes a bus whenever any one of the following three conditions are met:

- The wire is labeled with a netname with an array suffix. An array suffix consists of two numbers separated by a colon and enclosed in brackets. For example Data[0:7] means the bus consists of the eight nets Data[0], Data[1], up to Data[7].

- The wire is connected to the wide end of a BUS tap (main menu Edit->Place BUS tap).

A net connected to the other end, the pointed end of a tap, is called a tap net, and is an individual net from the nets represented by the bus. Tap nets must be labeled with an individual array element suffix (a single number without colon enclosed in brackets). For example Data[3] would be the label of a tap net out of the Data[0:7] bus. - The net is connected to a bus pin of a component that has an array type name.

Once a wire is becoming a bus it is automatically drawn with extra thick lines.

A bus may be automatically connected (netlisted) to a corresponding array of components. An array of components is created by appending a bracketed array specifier to the instance name (reference designator) of a bus-connected single component. For example, instead of naming a transistor Q1 naming it Q[1:4] would result in the single symbol representing four identical transistors. The base, collector and emitter pins of these component array all need to be connected to busses. For example to busses called Base[1:4], Collector[1:4], and Emitter[1:4]. The resulting netlist is arbitrary if the pins of a component array are not properly connected to busses, but e.g. accidentally to single nets only.

Note that recursive connections are possible around a single device or device group through the use of appropriate net labeling. For example', a single digital DFLOP device may be annotated to represent a 64 shift-register string by:

- adding a 64 element array suffix to its instance name, e.g. A1 would become A1[0:63],

- placing on its D input a corresponding array net label, e.g., Data[0:63] (the particular name is unimportant), and

- placing on its Q output an appropriately displaced array net label, e.g., Data[1:64].

The result would be that the D inputs of A1[1] to A1[63] are connected to the Q outputs of A1[0] to A1[62]. The D input of A1[0] (Data[0]) and Q output of A1[63] (Data[64]) need to be tapped off individually from the bus, and would represent the input and output of the resulting 64 bit shift register.

- Example Notes:

- As usual for any flip-flop, a delay parameter must be specified in the Value field, e.g., td=10ns.

- The D input to the first gate may be individually accessed by its appropriate array index, e.g., Data[0]

Title Block

The schematic editor can display a special symbol as a title block. This is a combined feature of the schematic editor and the symbol editor. The feature is purely cosmetic. It allows to decorate a schematic so it looks more like a traditional drawing (depending on what is actually in the title block symbol).

The title block needs to be created in the form of a symbol (.asy file), and be of symbol type MASTER. However, the LTspice symbol editor does not allow the creation of a symbol with such a type, while editing such a symbol is possible. Therefore, it is initially necessary to created an empty MASTER symbol with a text editor. Once initially created it can be opened and edited in LTspice.

To start it is enough to create a .asy file with the following two lines in a text editor

Version 4 SymbolType MASTER

Once saved from the text editor the file can then be opened in LTspice and the drawing commands can be used to design the title block, e.g. a frame, and several text fields. Pins must not be added to a title block symbol. Once saved in a project's directory, the title block can be added to a schematic just like any other symbol.

Since it is difficult to edit a schematic while a title block is visible (attempting to select a component results in the selection of the title block instead), the title block may be turned on and off via the following option.

View->Control Panel->Drafting Options->Show Title Blocks

Before printing a page with a title block it is advisable to adjust the zooming of the schematic in the schematic editor, so the schematic with the title block exactly fits the screen. This can be done either via the toolbar button "Zoom full extents" or the menu item View->Zoom to fit. This assumes every symbol has been drawn within the boundaries of the title block.

Here is an example of a simple title block symbol File:Title-block.asy.

Symbol Editor

Key Combination

- (since end of October 2012 release) Clicking Alt-Left on a label in the plot pane highlights the corresponding node in the schematic. E.g. clicking Alt-Left on a label like V(n001) in the plot pane highlights the n001 node. Clicking Alt-Left on a label like I(R1) highlights R1 in the schematic.

Placing the "LT" Logo within a Symbol

The text LT (all uppercase) in a symbol (menu Draw->Text) is replaced with the Linear Technology logo when the symbol is used on a schematic.

Cut & Paste Between Symbols

Unfortunately this has yet to be implemented. Two workarounds are possible, but they are both cumbersome.

- Open the symbol you wish to copy, then immediately save it with a new name. Modifying first before saving is dangerous because this requires always remembering to change the name after a distracting editing process. However, if the original is inadvertently overwritten, as long as the file is not closed the original may be recovered by repeatedly pressing the Undo key and then resaving.

- Use a text editor to open both symbol files and copy the ASCII drawing command sequences from one file to the other. The commands are not difficult to read for selective editing, but the entire sequence also may be copied over and then subsequently graphically cleaned up from within LTspice's symbol editor.

Plotting

Eye Diagram

LTspice can plot eye diagrams - a feature which is only semi-documented. The following two "Plot Settings" menu items related to eye diagrams

[select a plot pane (.raw)] Plot Settings->Eye Diagram->Enable Plot Settings->Eye Diagram->Properties

They are usually disabled. LTspice enables them when adding the insufficiently documented, baudrate-option

.option baudrate=<rate>

to a schematic. Instead of <rate> the nominal symbol rate of the signal should be given. <rate> defines at what intervals the signal should be triggered.

Once enabled the

Plot Settings->Eye Diagram->Properties

menu item allows to set two more eye diagram properties. An initial delay, which effectively specifies where the eye(s) should be plotted on the horizontal axis. And the number of eyes, which is equivalent how many trigger intervals should be displayed.

The following schematics both contain a baudrate option, but it is commented out.

examples/Education/PLL.asc examples/Education/PLL2.asc

Uncommenting the option, running the simulation, enabling the eye diagram in the Plot Settings, and then probing the signal net (not the out net) gives a typical eye diagram.

Probing Subcircuit Waveforms (signal naming conventions)

To be able to display subcircuit waveforms, you must first ensure that the Save Subcircuit Node Voltages and the Save Subcircuit Device Currents options are enabled in the Save Defaults tab of the Control Panel. Then, if your simulation was created as a hierarchical design using LTspice's Schematic Capture window, you may simply use the probe tool to select an active subcircuit schematic's nodes as required. But if the SPICE netlist was imported from an external source then the probe statement format is as follows:

- a top level node:

.probe v(node)

- a subcircuit node:

.probe v(subckt_name:node) .probe v(subckt_name:subsubckt_name:node)

- a subcircuit MOSFET drain current:

.probe id(subckt_name:mp1)

Netlists

A netlist line starting with "*!LTspice: " is now treated as a SPICE directive for LTspice (but a comment in other SPICE programs). - 09/05/06

References & Footnotes

- ↑ Other SPICE versions have no such problem with time